?計算機組成原理2017年4月真題試題(02318)

摘要:計算機組成原理2017年4月真題試題及答案解析(02318),本試卷總公共150分鐘。

計算機組成原理2017年4月真題試題及答案解析(02318)

計算機組成原理2017年4月真題試題及答案解析(02318),本試卷總公共150分鐘。

一、單項選擇題

(本大題共15小題,每小題1分,共15分)在每小題列出的四個備選項中只有一個是符合題目要求的。請將其代碼填寫在題后的括號內。錯選、多選或未選均無分。

1.計算機中完成對指令譯碼的部件是

A.運算器

B.控制器

C.存儲器

D.輸入輸出設備

2.在計算機內部表示指令和數據的最終形式是

A.二進制數

B.八進制數

C.十進制數

D.十六進制數

3.一個可執行程序在啟動運行時存放在

A.控制器

B.主存儲器

C.輔助存儲器

D.運算器

4.若十進制數為-85,則其對應的8位補碼[X]補為

A.01010101

B.10101010

C.10101011

D.11010101

5.下列軟件中不是系統軟件的是

A.UNIX

B.Oracle

C.Office

D.Visual studio

6.在采用立即尋址方式的指令中,操作數在

A.指令中

B.通用寄存器中

C.內存中

D.外存中

7.下列關于指令系統的說法正確的是

A.RISC指令系統比CISC指令系統復雜,指令條數多

B.CISC指令系統指令周期比RISC指令系統指令周期短

C.RISC指令系統中指令的長度一致

D.CISC指令系統計算機采用硬連線控制器

8.MIPS計算機的匯編指令“and$sl,$s2,$s3”的功能是

A.$s3=$s1+$s2

B.$s1=$s2+$s3

C.$s2=$s1+$s2

D.$s1=$s2&$s3

9.下列關于異常和中斷的描述中,錯誤的是

A.中斷是由CPU之外的部件觸發的事件

B.中斷是與CPU當前執行指令無關的異步事件

C.異常是與當前執行指令相關的同步事件

D.異常是可以由CPU通過屏蔽字進行屏蔽的事件

10.存放微程序的控制存儲器包含在

A.堆棧存儲器中

B.主存儲器中

C.控制器中

D.運算器中

11.一個8KB的存儲器,按字節編址需要地址線

A.11條

B.12條

C.13條

D.14條

12.在計算機的存儲器層次結構中,速度最快的是

A.硬盤

B.寄存器

C.高速緩存

D.主存

13.在采用奇校驗編碼時,一組數據位與校驗位中共包含有

A.奇數個“0”

B.奇數個“1”

C.偶數個“0”

D.偶數個“1”

14.在計算機中將運算器和控制器合稱為

A.主機

B.外設

C.ALU

D.CPU

15.下列尋址方式中,獲取操作數最慢的是

A.直接尋址

B.間接尋址

C.寄存器直接浮址

D.相對尋址

二、填空題

(本大題共19空,每空1分,共19分)請在“答題卡”填上正確答案,錯填、不填均無分

11.存儲器分為內存和外存,而內存包括_________和________

12.在 Intel的CPU中將內部異常分為________、________和________三類。

13.根據能否由屏蔽字來屏蔽,中斷分為________和________兩類。

14.兩個8位二進制整數的補碼01101001和00010111相加后,標志位CF=________,SF=________,OF=________,ZF=________

15.解決 cache與主存一致性問題的 cache寫操作一般有________和________兩種。

16.計算機系統總線包括________線、________線和________線。

17.中斷服務程序一般包含三個階段,分別是________階段、________階段、________階段。

三、名詞解釋題

(本大題共4小題,每小題3分,共12分)

21.易失性存儲器

22.尋址方式

23.DMA控制器

24.系統程序員

四、簡答題

(本大題共3小題,每小題5分,共15分)請在答題卡上作答。

31.簡述計算機中多字節數據存儲時,大端和小端存儲方式的差異。

32.簡述CISC指令系統的特點。

33.為什么動態存儲器需要刷新?

五、計算題

(本大題共3小題,每小題5分,共15分)

41.某計算機的時鐘頻率為2.5GHz,指令集中有A~E五種不同類型的指令,這五類指令的平均時鐘周期數CPI分別為3、2、4、5、3。設有一程序P的指令序列中,五類指令所占比例分別為20%、28%、22%、10%、20%(1)該計算機的峰值MIPS是多少?(2)該計算機執行程序P的平均時鐘周期數CPI是多少?

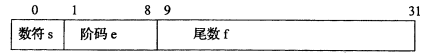

42.將計算機中用IEEE74單精度浮點數格式表示的機器數(BFB00000)16轉換成十進制真值。注:IEE754單精度浮點數的計數公式為(-1)8×1.f×2e-127,IEEE754單精度浮點數的機器數格式如下:

43.設有同步總線寬度為32位,時鐘頻率為80MHz,一個時鐘周期傳送一次數據,該總線的帶寬是多少MB/s?如果對總線進行改進讓其一個時鐘周期能傳送4次數據,時鐘頻率降低到60MHz,則總線的帶寬是多少MB/s?

六、綜合題

(本大題共2小題,每小題12分,共24分)

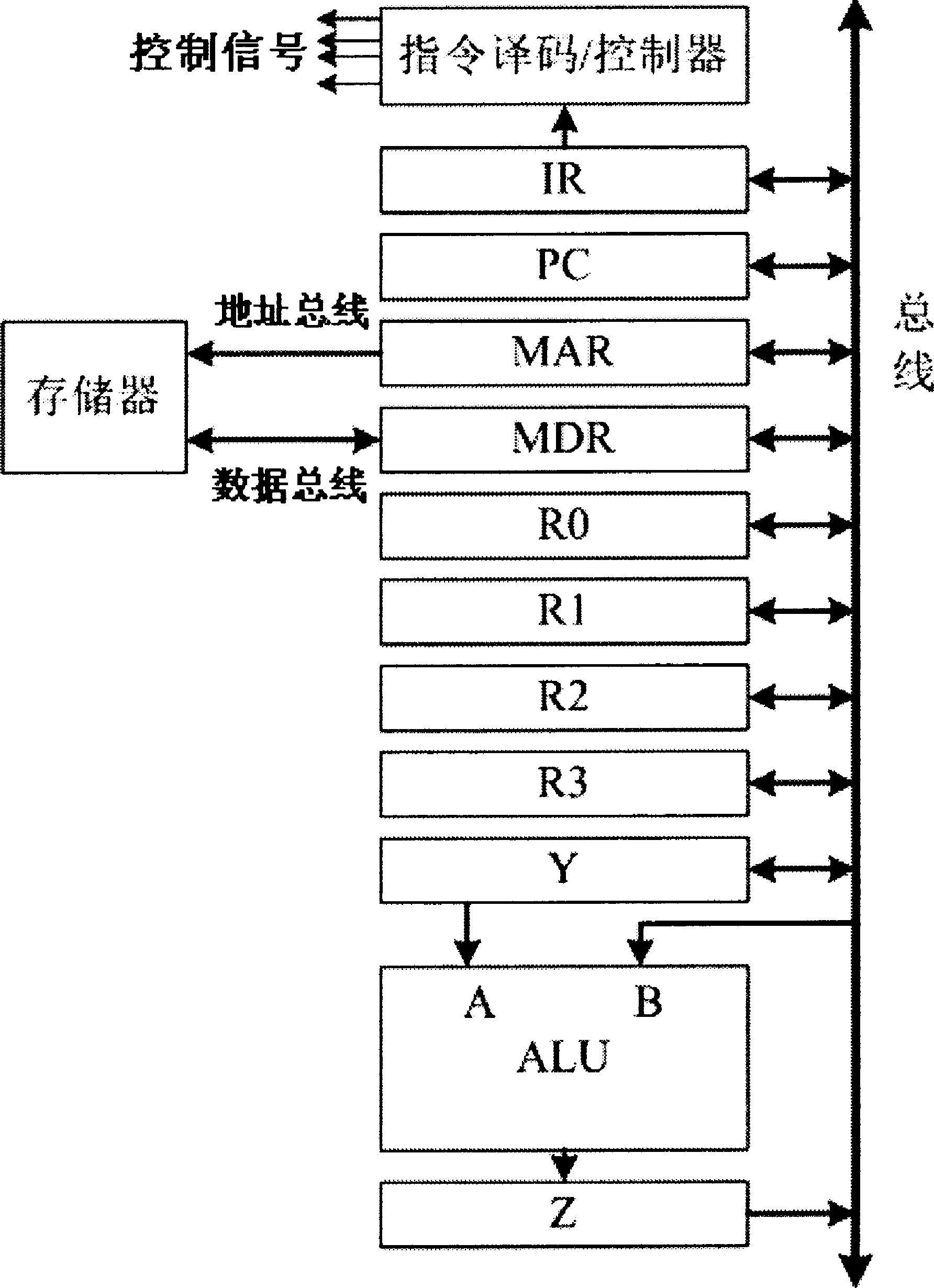

51.某計算機字長16位,釆用16位定長指令格式,部分數據通路結構如圖所示。假設MAR的輸出一直處于使能狀態。(1)減法指令“SUB R1,R2”在執行階段需要多少個節拍?注:該指令功能為R1的內容減去R2的內容,結果送入R1中。(2)寫出每個節拍的功能和有效控制信號。

52.某計算機主存地址空間大小32MB,按字節編址。主存與 Cache之間采用全相聯映射方式,塊大小為512字節。 Cache數據區大小為8KB。問:Cache共有多少行?主存地址如何劃分?(要求說明每個字段的含義、位數和在主存地址中的位置。)

延伸閱讀

- 考前自救指南:希賽自考題庫快速提分

- 自考專屬刷題工具,刷題即提分!

- 最后9天,自考歷年真題應該怎么刷?

- 自考備考一站式服務:希賽自考題庫APP

- 0基礎逆襲秘籍:希賽全套自考學習包(含智能題庫)

- 避開備考誤區!用希賽自考APP快速提分!

自考微信公眾號

掃碼添加

自考備考資料免費領取

去領取

掃描二維碼

掃描二維碼