軟考嵌入式系統設計師考試經典100題21-30

摘要:軟考嵌入式系統設計師考試經典100題由希賽網整理,本文是軟考嵌入式系統設計師考試經典100題的21-30題內容,以便考生對嵌入式系統設計師考試知識點的掌握檢測。

為方便軟考考生對嵌入式系統設計師考試知識點的檢測,希賽軟考頻道為考生整理了軟考嵌入式系統設計師考試經典100題的資料,本文是軟考嵌入式系統設計師考試經典100題的21-30題內容(100題及答案解析完整版可在本文文首本文資料處或文末的資料下載欄目下載):

21、以下關于嵌入式軟件開發的敘述中,正確的是( )。

A.宿主機與目標機之間只需要建立邏輯連接即可

B.調試器與被調試程序一般位于同一臺機器上

C.嵌入式系統開發通常采用的是交叉編譯器

D.宿主機與目標機之間的通信方式只有串口和并口兩種

22、數據結構反映了數據元素之間的結構關系。鏈表是一種非順序存儲線性表,它對于數據元素的插入和刪除( )。

A.不需要移動結點,不需要改變結點指針

B.不需要移動結點,只需要改變結點指針

C.只需要移動結點,不需要改變結點指針

D.既需要移動結點,又需要改變結點指針

23、堆是一種有用的數據結構,下列關鍵字序列中,( )是一個堆。

A.16,72,31,23,94,53

B.94,53,31,72,16,53

C.16,53,23,94,31,72

D.16,31,23,94,53,72

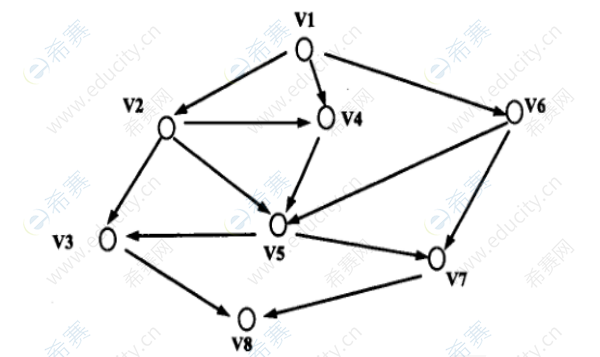

24、針對下圖所示的有向圖,從結點V1出發廣度遍歷所得結點序列和深度遍歷所得結點序列分別是( )。

A.v1,v2,v3,v4,v5,v6,v7,v8和v1,v2,v3,v8,v5,v7,v4,v6

B.v1,v2,v4,v6,v3,v5,v7,v8和v1,v2,v3,v8,v5,v7,v4,v6

C.v1,v2,v4,v6,v3,v5,v7,v8和v1,v2,v3,v8,v4,v5,v6,v7

D.v1,v2,v4,v6,v7,v3,v5,v8和v1,v2,v3,v8,v5,v7,v4,v6

25、若計算機存儲數據采用的是雙符號位(00表示正號、11表示負號),兩個符號相同的數相加時,如果運算結果的兩個符號位經( )運算得1,則可斷定這兩個數相加的結果產生了溢出。

A.邏輯與

B.邏輯或

C.邏輯同或

D.邏輯異或

26、數字電路根據邏輯功能的不同特點,可以分成兩大類:組合邏輯電路和時序邏輯電路。以下針對組合邏輯電路和時序邏輯電路的敘述中,不正確的是( )。

A.組合邏輯電路任意時刻的輸出取決于該時刻的輸入,與電路原來的狀態無關

B.時序邏輯電路任意時刻的輸出取決于該時刻的輸入以及電路原來的狀態

C.常見的組合邏輯電路有計數器、寄存器、順序脈沖發生器等

D.時序邏輯電路主要由存儲電路和組合邏輯電路兩部分組成

27、對于TTL電路和CMOS電路的原理及比較,以下描述中不正確的是( )。

A.TTL電路是電壓控制,CMOS電路是電流控制

B.TTL電路速度快,但是功耗大,CMOS電路速度慢,傳輸延遲時間長

C.CMOS電路具有鎖定效應

D.CMOS電路在使用時不用的管腳不要懸空,要接上拉電阻或下拉電阻

28、嵌入式處理器是嵌入式系統的核心,一般可分為嵌入式微處理器(MPU),微控制器(MCU),數字信號處理器(DSP)和片上系統(SOC)。以下描述中,不正確的是( )。

A.MPU在可靠性等方面做了各種增強,適用于運算量較大的智能系統設計

B.微控制器俗稱單片機,其品種數量非常豐富

C.DSP處理器對系統結構和指令進行了特殊設計,適合數字信號處理

D.片上系統設計的關鍵是IP核,IP核一般分為硬核、軟核和固核

29、以下關于馮?諾依曼結構和哈佛結構的描述中,不正確的是( )。

A.馮?諾依曼結構的計算機中程序和數據共用一個存儲空間

B.馮?諾依曼結構中程序計數器負責提供程序執行所需要的地址

C.哈佛結構的計算機在一個機器周期內可同時獲得指令字和操作數

D.哈佛結構中取指和執行不能完全重疊

30、I/O端口的訪問包括存儲器映射方式和I/O映射方式,下面描述中不正確的是( )。

A.存儲器映射方式是指對端口地址和存儲器統一編址

B.I/O映射方式是指對端口地址和存儲器分開獨立編址

C.存儲器映射方式中,對端口內容不能進行算術邏輯運算、移位等操作

D.I/O映射方式中需要使用專門的I/O指令對I/O端口進行操作

軟考高項紙質版資料領取活動來啦!

活動截止12月15日

趕緊掃碼參與活動吧!

熱門:信息系統監理師備考 | 網絡工程師備考 | 軟件設計師備考

推薦:信息系統項目管理師網絡課堂 | 2025下半年軟考真題答案及解析

課程:信息系統項目管理師報考指南 | PMP課程

延伸閱讀

軟考備考資料免費領取

去領取

- 1

- 6

- 5

專注在線職業教育24年

專注在線職業教育24年

掃描二維碼

掃描二維碼

掃描二維碼

掃描二維碼